다이소에서 싼 맛에 산

5천원 / 32GB / Axxen sd 카드가

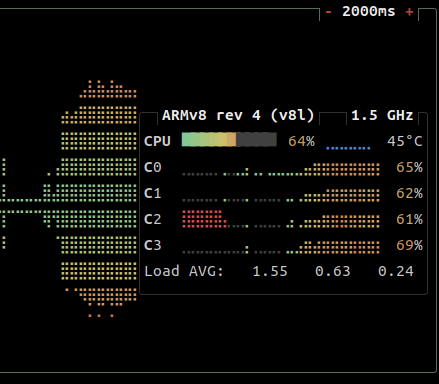

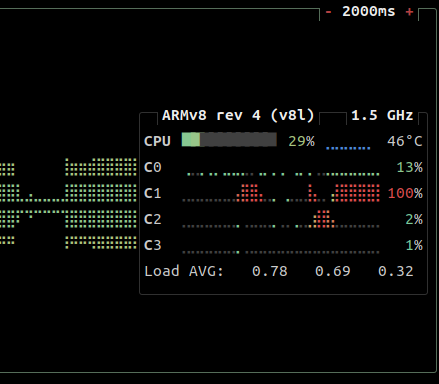

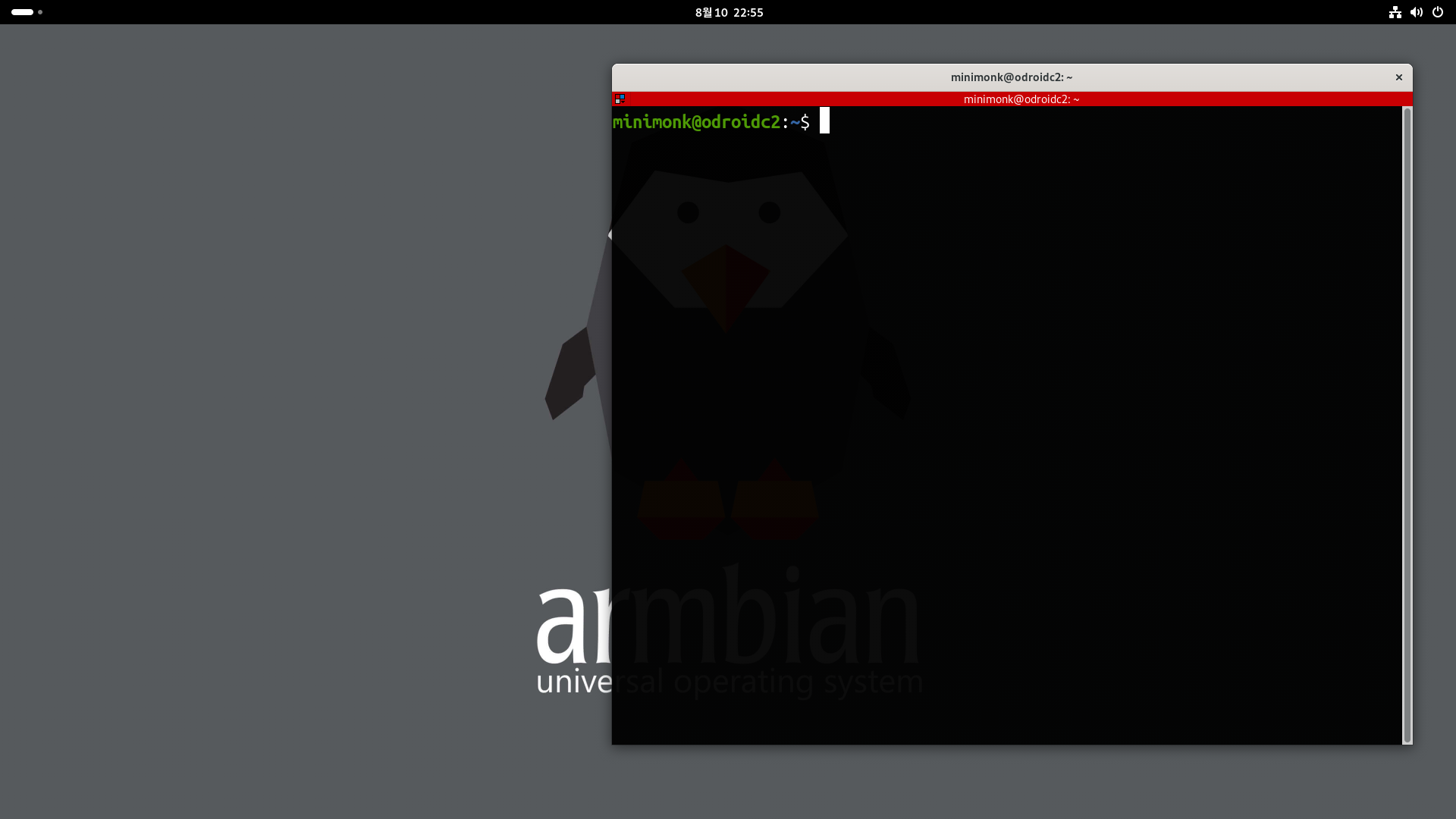

odroid c2 에서 armbian 으로 쓰는데 허구한날 먼가 하다가 날아간다.

2개 가서 두개가 번갈아 가면서 몇번 발생하거면

지지리도 운이 없거냐

axxen이 내구도가 안 좋거나

armbian이 문제거나..

에러메시지는 맨날 btrfs 에서 멈춰서 혹시나 해서 봤는데 ext 인디..

| $ mount sysfs on /sys type sysfs (rw,nosuid,nodev,noexec,relatime) proc on /proc type proc (rw,nosuid,nodev,noexec,relatime) udev on /dev type devtmpfs (rw,nosuid,relatime,size=835580k,nr_inodes=208895,mode=755) devpts on /dev/pts type devpts (rw,nosuid,noexec,relatime,gid=5,mode=620,ptmxmode=000) tmpfs on /run type tmpfs (rw,nosuid,nodev,noexec,relatime,size=196088k,mode=755) /dev/mmcblk0p1 on / type ext4 (rw,relatime,errors=remount-ro,commit=120) securityfs on /sys/kernel/security type securityfs (rw,nosuid,nodev,noexec,relatime) tmpfs on /dev/shm type tmpfs (rw,nosuid,nodev) tmpfs on /run/lock type tmpfs (rw,nosuid,nodev,noexec,relatime,size=5120k) cgroup2 on /sys/fs/cgroup type cgroup2 (rw,nosuid,nodev,noexec,relatime,nsdelegate,memory_recursiveprot) pstore on /sys/fs/pstore type pstore (rw,nosuid,nodev,noexec,relatime) bpf on /sys/fs/bpf type bpf (rw,nosuid,nodev,noexec,relatime,mode=700) systemd-1 on /proc/sys/fs/binfmt_misc type autofs (rw,relatime,fd=32,pgrp=1,timeout=0,minproto=5,maxproto=5,direct,pipe_ino=3927) hugetlbfs on /dev/hugepages type hugetlbfs (rw,nosuid,nodev,relatime,pagesize=2M) debugfs on /sys/kernel/debug type debugfs (rw,nosuid,nodev,noexec,relatime) mqueue on /dev/mqueue type mqueue (rw,nosuid,nodev,noexec,relatime) configfs on /sys/kernel/config type configfs (rw,nosuid,nodev,noexec,relatime) fusectl on /sys/fs/fuse/connections type fusectl (rw,nosuid,nodev,noexec,relatime) tmpfs on /tmp type tmpfs (rw,nosuid,relatime) binfmt_misc on /proc/sys/fs/binfmt_misc type binfmt_misc (rw,nosuid,nodev,noexec,relatime) /dev/mmcblk0p1 on /var/log.hdd type ext4 (rw,relatime,errors=remount-ro,commit=120) /dev/zram1 on /var/log type ext4 (rw,nosuid,nodev,noexec,relatime,discard) sunrpc on /run/rpc_pipefs type rpc_pipefs (rw,relatime) tmpfs on /run/user/1000 type tmpfs (rw,nosuid,nodev,relatime,size=196084k,nr_inodes=49021,mode=700,uid=1000,gid=1000) portal on /run/user/1000/doc type fuse.portal (rw,nosuid,nodev,relatime,user_id=1000,group_id=1000) |

commit=120은 2분에 한번 강제 저장인데

그렇다고 해서 무조건 또 저장이 되는건 아니라고

그런데. relatime 해놓고 commit 하면 sd 카드 수명 팍팍 갉아 먹는거 아닌가?

'embeded > odroid' 카테고리의 다른 글

| odroid c2 armbian / hdmi audio out 실패 (0) | 2025.09.22 |

|---|---|

| iperf3 설정별 속도 (0) | 2025.08.21 |

| 빌드하다가 시스템이 날아감 -_-! (0) | 2025.08.13 |

| odroid c2 opencv haar cascade / face_recognition (0) | 2025.08.12 |

| armbian X11-forwarding 활성화 하기 (0) | 2025.08.11 |