pynq가 더 싸게 팔리는데 차이가 없다면 pynq를 사서 arty 이미지를 써서 가지고 노는것도 방법일 듯?

| Between PYNQ Z1 and Arty Z7, the only difference is that the PYNQ has a microphone and Arty Z7 doesn't, otherwise they are identical from the specs point of view. |

[링크 : https://www.reddit.com/r/FPGA/comments/fkumbh/is_the_arty_a7_or_a_similarly_priced_zynq_board/]

arty z7의 경우

HDMI in / out이 있는게 장점 인듯.

'embeded > FPGA - XILINX' 카테고리의 다른 글

| zynq vitis openCL (0) | 2025.06.27 |

|---|---|

| EBAZ4205 zynq (0) | 2025.03.25 |

| xilinx vdma (0) | 2025.01.16 |

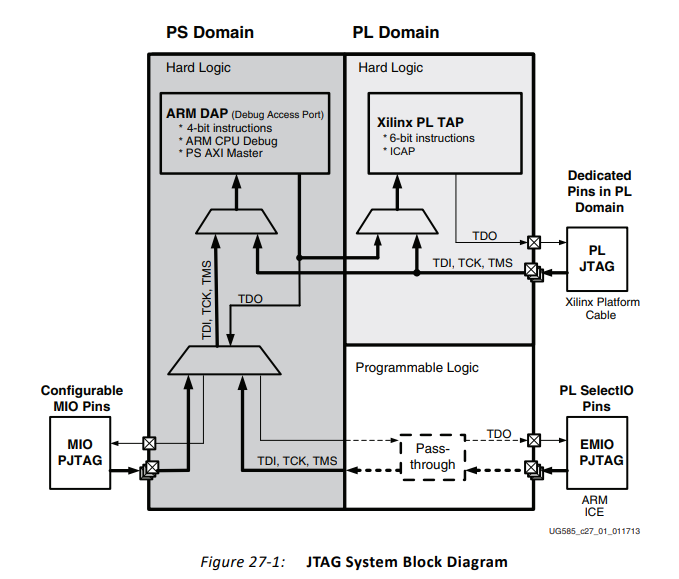

| ftdi jtag (0) | 2023.07.22 |

| xilinx zynq jtag (2) | 2023.07.21 |